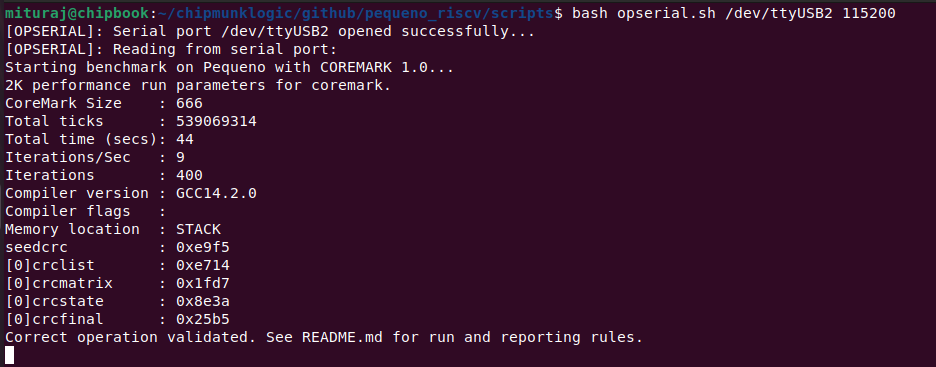

CoreMark® Results on Board

Report date: Sept 2025

Image path : coremark_run.png

| Processor | Pequeno RISC-V (PQR5), pqr5 v1.0.3 |

|---|---|

| Pipeline | 5-stage, inorder, single-issue |

| ISA | RV32I (no extensions) |

| CPU configuration | Performance++ |

| Target | FPGA, CMOD A7-35T Board, Artix-7, xc7a35tcpg236-1 |

| Core clock speed | 12 MHz |

| Compiler | riscv64-unknown-elf-gcc (GCC 14.2.0) |

| Compiler flags | -O3 -march=rv32i -mabi=ilp32 -ffreestanding -fno-builtin -fno-stack-protector -static -nostartfiles |

| Baremetal/OS | Baremetal |

| Memory | FPGA BRAMs for Instruction & Data, no cache |

| Instruction RAM size | 32 kB |

|---|---|

| Data RAM size | 8 kB |

| .TEXT | 0x00000000--0x80005894 | 22676 Bytes |

|---|

| .RODATA | 0x80000000--0x80000794 | 1940 Bytes |

|---|---|---|

| .DATA | 0x80000794--0x800007B8 | 36 Bytes |

| .BSS | 0x800007B8--0x000007C0 | 8 Bytes |

| Stack | 0x800007C0--0x80002000 | 6208 Bytes |

| CoreMark iterations | 400 |

|---|---|

| Execution time | 43 seconds |

| Iterations per second | 9 |

| CoreMark score | 0.77 CoreMark/MHz |

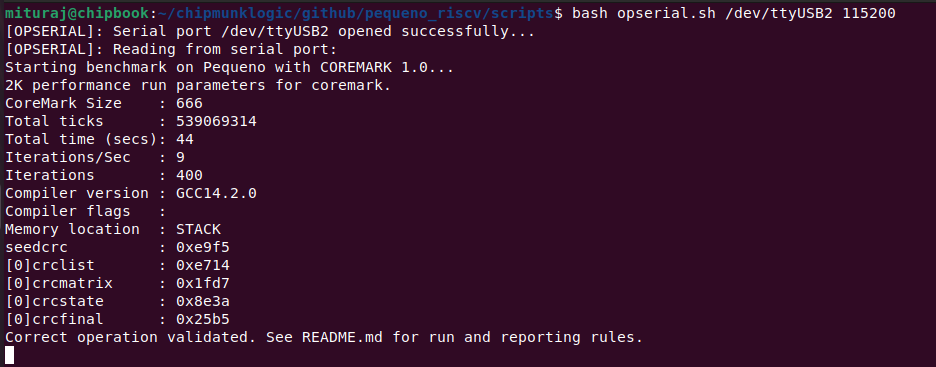

Report date: Sept 2025

Report date: Sept 2025

Image path : coremark_run.png

../build_notes.txt